PCIe/NVMe to Gen-Z Bridge: IPA-PE223A-BR

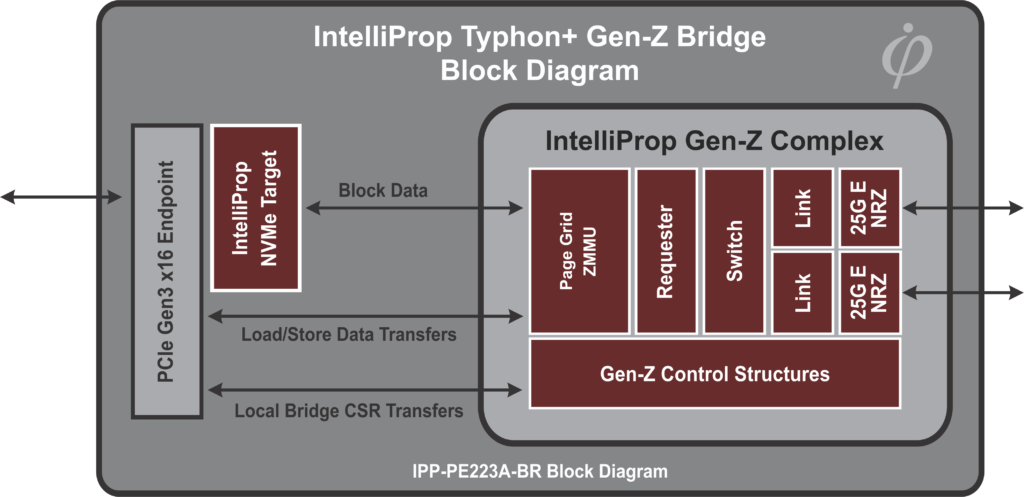

The IntelliProp IPP-PE223A-BR (code name “Typhon+”) PCIe/NVMe to Gen-Z bridge is an FPGA based application. The Typhon+ bridge has an NVMe target core attached to a PCIe endpoint core conforming to a standard NVMe device. The PCIe core is also configured to present a PCIe BAR for host memory mapped accesses. Both the NVMe I/O traffic and the BAR based memory traffic are targeted to a Gen-Z Requester subsystem via a standard and programmable Page Grid Gen-Z Memory Management Unit (ZMMU) interface. An additional BAR is present to the PCIe host to access and configure local Gen-Z bridge component structures, including the ZMMU page grid entries and page table entries.

Functional Description

The IPP-PE223A-BR PCIe/NVMe to Gen-Z Bridge provides an interface for a PCIe host system to utilize a Gen-Z fabric. Block level transfers are supported via a standard NVMe target core, and is compatible with industry standard NVMe OS drivers. Load/Store transfers are supported via a PCIe BAR mapped memory aperture. A custom Gen-Z bridge driver and application is also available supporting Gen-Z memory and Gen-Z block DMA operations, and providing advanced Gen-Z system configuration and management within a Linux operating system.

The IPP-PE223A-BR PCIe/NVMe to Gen-Z Bridge provides an interface for a PCIe host system to utilize a Gen-Z fabric. Block level transfers are supported via a standard NVMe target core, and is compatible with industry standard NVMe OS drivers. Load/Store transfers are supported via a PCIe BAR mapped memory aperture. A custom Gen-Z bridge driver and application is also available supporting Gen-Z memory and Gen-Z block DMA operations, and providing advanced Gen-Z system configuration and management within a Linux operating system.

Gen-Z destination mapping of both block level and load/store transfers is programmable via a Gen-Z compliant page grid ZMMU. In-band Gen-Z configuration is achieved via an additional PCIe BAR mapped to the local Gen-Z core structure and component structures.

An integrated Gen-Z switch provides two Gen-Z egress ports, allowing connection to multiple Gen-Z endpoints; either additional switches or Gen-Z devices. The switch layer IP core also enables end-to-end packet relay between Link Layers.

Device Support:

IntelliProp’s Typhon+ bridge is available for integration into the Xilinx XCVU9P FPGA implemented on the BittWare XUPP3R board. Support for other FPGA implementations available by request.

Applications for the PCIe/NVMe to Gen-Z bridge include

- Applications that require an industry compliant method to connect a PCIe host to a Gen-Z fabric

- Applications that require full Gen-Z feature and configuration support

IPP-PE223A-BR Features

- Utilizes proven IntelliProp IP cores for NVMe and Gen-Z functions

- Compliant with the Gen-Z 1.1 Core Specification and Gen-Z 1.1 Phy Specification

- Compliant to standard NVMe host OS drivers to transfer block level I/O transfers for Gen-Z unaware OS support

- Compliant to typical byte granularity memory transfers (e.g. linux mmap)

- Explicit Op-Class format support (Core64, Control, Atomic, etc.)

- Linux Gen-Z bridge driver and management applications available with Gen-Z aware OS support

- Single Subnet/Single Route destination packet routing support

- Single Subnet/Single Route packet relay support

- Multi-Action VC remapping support