Technology

What is Gen-Z?

Gen-Z is a high performance, low latency, memory-semantic fabric which can be used to communicate to every device in the system. It not only simplifies every interface but also provides the building blocks to create high performance low latency solutions where every device in the system are peers to one another and speak the same memory-semantic language. Gen-Z solutions will be free to scale with a diversity of compute, memory, and storage resources independently and exactly tailored to every workload and environment while ensuring interoperability and business agility.

Gen-Z is a high performance, low latency, memory-semantic fabric which can be used to communicate to every device in the system. It not only simplifies every interface but also provides the building blocks to create high performance low latency solutions where every device in the system are peers to one another and speak the same memory-semantic language. Gen-Z solutions will be free to scale with a diversity of compute, memory, and storage resources independently and exactly tailored to every workload and environment while ensuring interoperability and business agility.

Gen-Z differs from PCIe in that there can be multiple Root-Complex equivalents called requesters within a given fabric subnet. A Gen-Z device can be a requester, a responder or a requester/responder. In PCIe, you are either a Root Complex or an Endpoint which complicates CPU to CPU communication and slows down accelerators. With Gen-Z, every component on the Gen-Z fabric has equal access to the memory fabric.

Why is a new bus like Gen-Z needed?

Traditional techniques used to scale system solutions can no longer keep up

- Memory bandwidth per CPU core continues to decrease

- Memory capacity per core is generally flat

- Memory is changing on a different frequency compared to the CPU

- The number of memory components, memory channels and memory tiers can not be increased at the

- required rate

Data is growing

Exponential data growth is overwhelming traditional architectures

Data that requires real-time analysis is growing exponentially

The value of the analysis decreases if it takes too long to provide insights

The industry needs an open architecture to solve the problems

- Memory tiers will become increasingly important

- Rack-scale composability requires a high bandwidth, low latency fabric

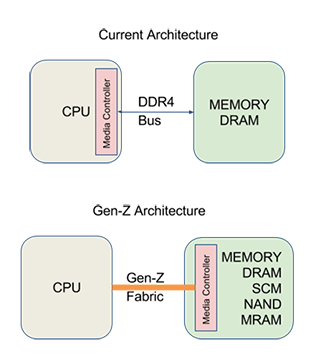

Gen-Z breaks the processor to memory linkage. In the past, for memory to scale, processors also needed to be added. But once memory is disaggregated from the processor as it is in Gen-Z, memory can now scale independently of the processor. This is able to occur because Gen-Z supports a split memory controller architecture. The memory controller functions virtually the same as it does today. The difference is that media specific functions are offloaded to the Media Controller which is located on the media device. This simple change has multiple benefits.

This abstraction of the memory media allows for mixed media types (volatile and non-volatile) to co-exist behind a transparent or abstracted media controller. The different types of media can scale as required by the application independent of each other. Gen-Z memory is mapped into the processors address space by system firmware. Once mapped, applications can access Gen-Z mapped memory components on the Gen-Z Bus the same as an other processor mapped memory. The read and write requests are transmitted across the Gen-Z bus and the media controller will translate these requests into media specific operations. Gen-Z memory components can support multiple links through a Gen-Z switch which allows multiple processors to directly map and access the various types of media located on the media cards. Thus allowing processors to flex the amount of DRAM, NAND, or other memory type required depending on their workload.

Additionally, certain media operations can be offloaded (accelerated) by the media controller directly. This allows the data to remain within the media controller boundary and not need to be copied into the processor cache for manipulation. This improves latency and application performance.

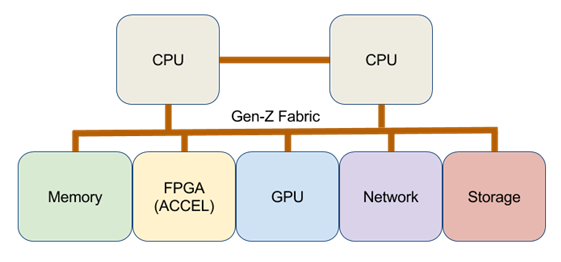

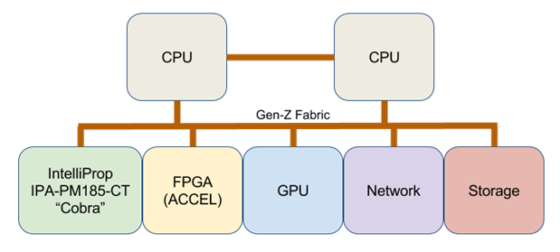

Looking at the Gen-Z fabric architecture, shown below, one can see where a Media Card would sit on the Gen-Z bus. Media cards utilizing the IntelliProp Gen-Z Hybrid Memory Controller “Cobra” to build a mixed DRAM/NAND memory module can be an equal member on the Gen-Z bus and accessed by any processor, GPU or other device on the bus.

Gen-Z allows for diverse component types to co-exist on the Gen-Z bus and to directly communicate without the need for intermediate interconnects or software. All nodes on the bus are equal.

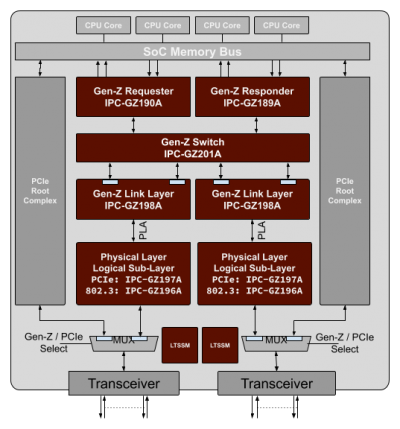

SoC Dual Boot PCIe / Gen-Z

The diagram shows a mixed PCIe Root Complex and Gen-Z Requester / Responder protocol stack inside of a SoC. This “dual-boot” application example shows how new CPU / SoC designs can be made to allow for both PCIe root complex and Gen-Z protocols sharing the same gigabit-transceivers. The SoC firmware can configure the IO interface to be a mixed PCIe Root Complex / Gen-Z complex, a dual port PCIe Root Complex, or a dual port Gen-Z complex. This flexibility allows SoC designers to leverage the Gen-Z fabric for specific applications while allowing for support of legacy PCIe components within the system.

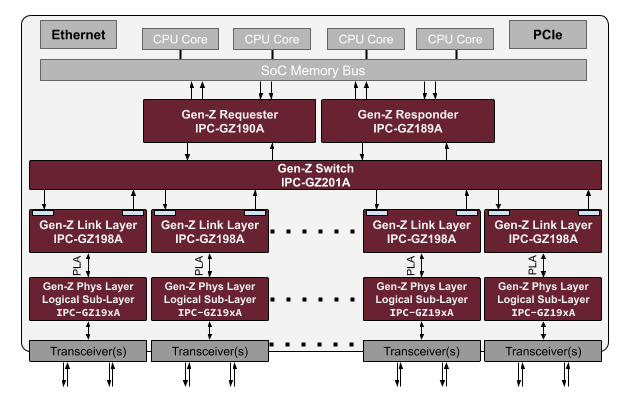

Gen-Z Switch

The diagram shows a multi-port Gen-Z switch created from IntelliProp IP building blocks. The Gen-Z switch is a key component within the Gen-Z ecosystem allowing for multiple processors / SoC to share and provision memory resources in a secure and low latency manor. The switch may be implemented in both FPGA and ASIC designs. The below diagram shows a switch with integrated Gen-Z requester and responder blocks along with a PCIe endpoint allowing bridging from legacy SoC hosts which do not have native Gen-Z interfaces.

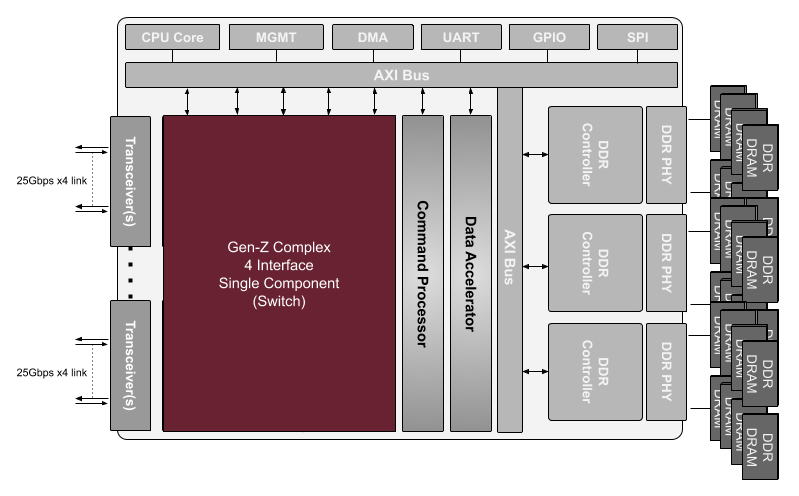

Gen-Z Media Controller

The diagram shows an example Gen-Z media controller with NAND flash created from IntelliProp IP building blocks. The Gen-Z media controller is a key component within the Gen-Z ecosystem allowing for multiple processors / SoC to share and provision memory resources in a secure and low latency manor. The media controller may be implemented in both FPGA and ASIC designs. The below diagram shows a media controller with both DRAM and NAND flash. This could be implemented in a manner similar to SATA / SAS / NVMe SSD using the Gen-Z block commands, or in a manner more similar to an NVDIMM device using Gen-Z byte addressable commands.